Data converters remain one of the most critical components in many modern electronic applications. The need to faithfully preserve the signal across domains continues to pressure data converters to deliver more bandwidth and linearity while reducing the power consumption. Recently, we noticed the development of exciting new architectures and circuits that push data converters towards higher performance. MICAS has always been a highly valued contributor in this domain, and this trend continues as we are working on a variety of architectures (time-interleaved pipeline-SAR ADCs, continuous-time sigma-delta ADCs, VCO-based ADCs, etc.) for a variety of applications (high-speed wireline, direct-RF sampling receivers, high-resolution sensor readout, imagers, etc.).

The trend at major solid-state circuit conferences is to use so-called figures-of-merit to compare different ADCs with each other. These figures-of-merit try to combine the speed, the accuracy, and the power consumption in a single number. The consequence of focusing on this number is that many researchers avoid implementing critical periphery circuits of a data converter. For example, the input buffer, the reference buffers, or the clock generation are often not included. However, it has been shown recently that this results in a highly optimized converter core, while the complete system, including these periphery blocks, would be entirely dominated by them. It is thus essential to include the periphery block in the design of the converter.

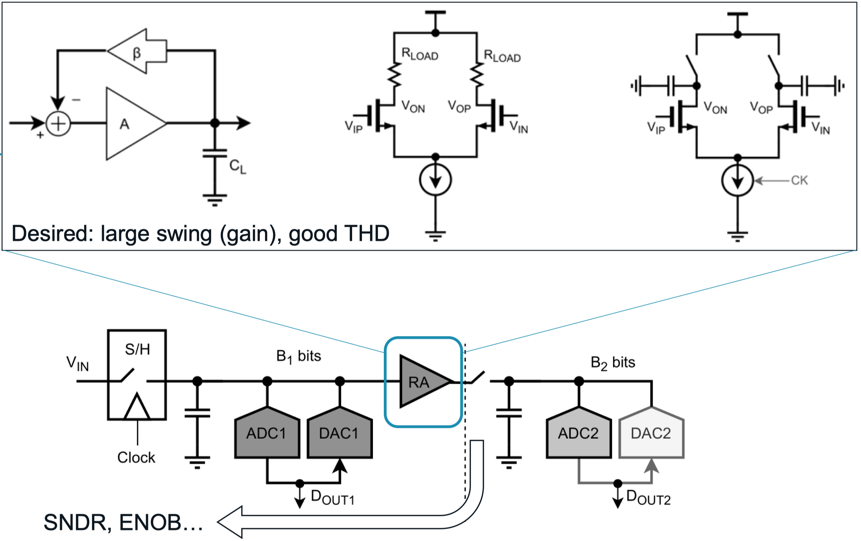

Dynamic circuits are very power efficient thanks to the scaling of their power consumption with the clock frequency. Additionally, open-loop circuits are high-speed and power-efficient, thanks to their lack of stability requirements. However, dynamic and open-loop circuits suffer from a lack of accuracy and a significant dependency on process variations. However, the ongoing trend is to use such dynamic, open-loop circuits and rely on heavy calibration to compensate for the lack of accuracy and process dependency. This evolution results in converters that perform exceptionally well in the measurement lab, while they are not useful in an actual application. We try to bridge this gap by innovating on the architectural and circuit level.

Traditionally, data converters operate in the voltage domain. Due to the reduced supply voltages of scaled technologies, this results in a reduced dynamic range or a higher power consumption. One of the recent proposals to avoid this evolution is to use frequencies or time delays within the converter. These VCO-based or time-based ADCs have a promising behavior, especially as transistors become faster. Thus, the frequency can increase, or the time delay can decrease, both increasing the resolution. MICAS is active in such novel types of converters for a broad range of applications.

Current research topics

Current research topics