AnalogCreate is a project under the ERC Advanced Grant scheme, under the leadership of professor Georges Gielen.

ABOUT THE PROJECT

Progress in semiconductor technology and in intelligent data processing are converging today, opening the door to countless smart ICT applications through the Cloud and Internet of Everything, to the people’s benefit in years to come. Applications that interact with the physical world (e.g. environmental sensing, healthcare, autonomous vehicles, etc.), also need analog integrated circuits in the cyber-physical or edge layer. But while digital circuits are largely synthesized automatically through software, the analog circuits are mainly still handcrafted in industry with low design productivity. This results in long and error-prone design cycles, and the high development costs jeopardize many potential new ICT applications from ever being realized (e.g. solutions for rare diseases). It becomes even more problematic when moving to advanced technologies below 16 nm CMOS, that come with way more design and layout rules to be dealt with. The showstopper for state-of-the-art analog synthesis tools is that they require design heuristics and constraints to be entered explicitly by designers in order to handle the humongous solution space and to steer the circuit and layout optimizations towards acceptable solutions. The proposed disruptively new approach is to use the self-learning capabilities of advanced machine learning algorithms to self-learn and then exploit the design expertise and constraints from the many available successfully completed designs. Also a true circuit topology synthesis approach will be developed to create a proper (possibly novel) schematic from the target specifications, as well as an innovative formal analog design verification approach based on Quick Error Detection. These innovations will enable for the first time ever to truly autonomously create analog circuits from specifications to fully verified layout without direct input from any designer in the loop, and therefore enable the affordable implementation of many promising ICT applications.

ABOUT ERC

The European Research Council (ERC) funds the very best scientists in Europe to perform novel and groundbreaking research, enabling disruptive innovations with high impact for society, on a scale and with a prestige that was unprecedented.

BINGO is a project under the ERC Consolidator Grant scheme, under the leadership of professor Marian Verhelst.

ABOUT THE PROJECT

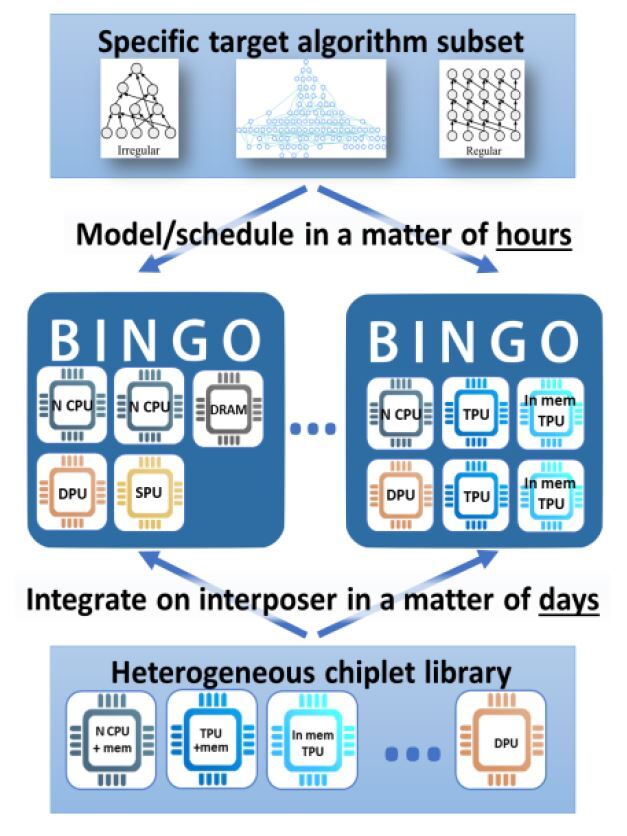

The next wave of smart applications in our society will need embedded devices (robots, wearables, etc.) with increased intelligence at much reduced energy and latency cost. Compared to current embedded platforms, up to 1000x efficiency gains could be achieved through tight processor-algorithm co-optimization. However, due to the slow development cycle of processor chips (many months to years) in comparison to algorithms (hours to weeks), this co-optimization today merely boils down to selecting algorithms which run well on mature, available hardware. As these processors and their tooling have been optimized for mature algorithms, not the inherently best algorithm “wins”, but the one that happens to best fit the available “old-school” hardware platforms. This “hardware lottery” holds back innovation, severely impacts embedded AI execution efficiency, and narrows the market to a few large companies.

The BINGO vision to break this innovation deadlock is to enable heterogeneous compute platform customization for a given AI workload in a matter of days (100x faster), through rapid selection and assembly of prefabricated co-processor chiplets. This needs breakthroughs in: a.) A library of embedded-AI-optimized co-processor chiplets, surpassing the SotA in terms of dataflow heterogeneity for improved efficiency (100x over CPU); and inter-operability in heterogeneous chiplet meshes on a reusable “breadboard” interposer. b.) Rapid cost models and workload schedulers for beyond-SotA heterogeneous platform customization: automatically deriving the optimal chiplet combination for an application, assemble it and deploy, all in a few days. Optimizing across the disciplines of chip design, computer architecture, scheduling, and AI fits perfectly to my expertise gained at KU Leuven, imec and Intel. It will stimulate a surge of embedded AI innovations, enable efficient execution of new algorithms, and bring the EU back at the forefront of chip design and embedded AI research.

ABOUT ERC

The European Research Council (ERC) funds the very best scientists in Europe to perform novel and groundbreaking research, enabling disruptive innovations with high impact for society, on a scale and with a prestige that was unprecedented.

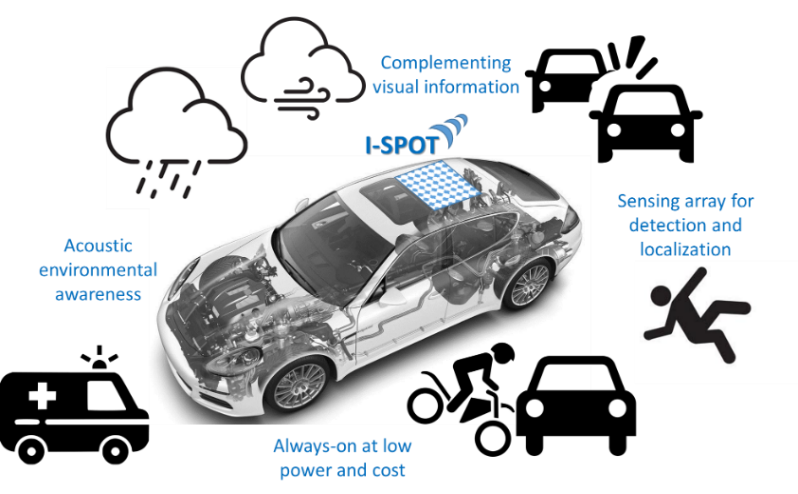

The I-SPOT project is an EU H2020 project sponsored under the MSCA-ITN-EID scheme (Project Reference: 956962). This European Industrial Doctorate program is a collaboration between KU Leuven and Bosch.

The goal of I-SPOT is to drive acoustic awareness of smart cars from two different angles:

1. As its technical contribution, I-SPOT aims to enable sensing, localizing and analyzing environmental audio signals during the active (drive) and passive (park) car mode by performing R&D on the following aspects:

· the efficient placement of audio sensors on the car body to improve the received signal quality

· the development of low-footprint signal processing technologies for automotive acoustic signal characterization and localization

· the design of smart, adaptive, ultra-low-power hardware that can be always-active, also when the car is switched off

2. The industrial/economical ambition of I-SPOT is to train young scientists in the field of low-power signal processing technologies and hardware for automotive applications, to:

· strengthen the position of Europe in the smart car electronics business

· transfer the relevant know-how to industry by educating scientists who apply the academic knowledge in a real industrial environment